|

Operand, 묵시주소, 즉치주소, 직접주소, 레지스터주소, 간접주소, 변위주소, 지정방식분류 |

I. 명령어 비트 제한의 효율적 활용, CPU 주소지정방식의 개요

가. 주소지정방식의 정의

|

- 연산에 사용될 데이터를 기억장치의 어디에서 가져올 것인가를 Operand 부분에 지정하는 방식 - 컴퓨터의 동작은 기억장치에 기억되는 명령어에 의해 실행 |

- 오퍼랜드 주소결정방식은 기억장치주소, 레지스터번호, 데이터 등의 정보를 활용하여 수행

II. CPU 주소지정방식의 종류 (묵즉 직레 간레 변)

가. 0주소 및 1주소 지정방식

|

지정방식 |

개념도 |

설명 |

|

묵시주소, 0주소 (Implied Mod) |

|

- 위치가 묵시적으로 포함 - 스택 구조 항상 상위 |

|

즉치주소, 0주소 (Immediate) |

|

- 데이터가 명령어에 직접 포함 - 명령어를 연산에 사용 |

|

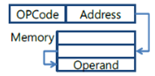

직접주소, 1주소 (Direct Address) |

|

- 연산 사용 데이터가 기억장치의 유효주소 - 오퍼랜드 길이보다 큰 데이터 사용 가능 |

|

레지스터, 1주소 (Register) |

|

- 연산 사용 데이터가 내부 레지스터에 저장 - 명령어의 오퍼랜드가 해당 레지스터 지정 |

- 1 주소 명령어의 경우 하나의 연산 대상은 AC에 있고 나머지 주소로 연산 대상을 지정

나. 2주소 및 3주소 지정방식

|

지정방식 |

개념도 |

설명 |

|

간접주소, 2주소 (Indirect Address) |

|

- 오퍼랜드 기억장치 주소 데이터는 실제 데이터 주소 지정 |

|

레지스터 간접주소 (Register Indirect) (2주소) |

|

- 오퍼랜드에서 지정하는 레지스터 내용을 실제 저장되어 있는 메모리의 주소를 저장 - 고속 참조 가능 |

|

변위주소, 3주소 (Displacement) |

|

- 오퍼랜드 필드를 직접주소와 오프셋으로 구성하여 실제 데이터 주소 결정 - 사용 효과적이나 변위 추가 작업 필요 |

- 주소방식에 따른 자료 접근 속도: 즉치>레지스터>직접>레지스터 간접>간접

III. CPU 주소지정방식의 오퍼랜드 결정 방식

- 기억장치 주소, 레지스터 번호, 데이터

'IT기술노트 > 컴퓨터구조 및 운영체제' 카테고리의 다른 글

| 제어장치(Control Unit) (0) | 2021.03.10 |

|---|---|

| 다중버스 계층구조 (0) | 2021.03.10 |

| 시스템버스 (0) | 2021.03.10 |

| TPC(Transaction Procession Performance Council) (0) | 2021.03.10 |

| EISC(Extensible Instruction Set Computer) (0) | 2021.03.10 |

| RISC(Reduced Instruction Set Computer) (0) | 2021.03.10 |

| CISC(Complex Instruction Set Computer) (0) | 2021.03.10 |

| Stored-program computer (0) | 2021.03.10 |

댓글