반응형

|

고정길이 명령어 구조, Hardwired, 캐시 분리 |

I. RISC의 개요

가. RISC(Reduced Instruction Set Computer)의 정의

|

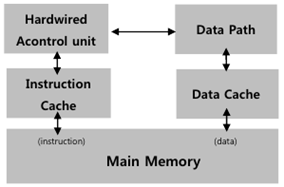

- 명령어의 수와 주소지정 방식을 최소화하여 제어장치의 구조를 간단하게 구성한 프로세스 구조 - 데이터 캐시와 명령어 캐시를 분리하여 사용 - Hardwired(하드웨어 내장) 방식 |

나. RISC의 명령어 집합구조

|

- 고정된 길이의 명령어 구조 à 파이프라인 적용 용이, CPI 상승 à 반면 프로그램의 복잡도 상승 |

II. RISC의 특징

- 고정길이 명령어 사용, 하나의 명령어가 단순한 기능 수행, 유사한 명령어 통합, 하드웨어 복잡도 낮춤

III. RISC의 문제점

- CPU 측면에서 활용도를 높이고, 고정 길이를 통한 파이프라인을 적용하였지만 역으로 고정길이에 따른 다양한 주소 모드나 Operand의 확장이 어려움

반응형

'IT기술노트 > 컴퓨터구조 및 운영체제' 카테고리의 다른 글

| 시스템버스 (0) | 2021.03.10 |

|---|---|

| TPC(Transaction Procession Performance Council) (0) | 2021.03.10 |

| CPU 주소지정방식 (0) | 2021.03.10 |

| EISC(Extensible Instruction Set Computer) (0) | 2021.03.10 |

| CISC(Complex Instruction Set Computer) (0) | 2021.03.10 |

| Stored-program computer (0) | 2021.03.10 |

| 하버드 아키텍처(Harvard Architecture) (0) | 2021.03.08 |

| 폰노이만 아키텍처 (0) | 2021.03.08 |

댓글