반응형

중앙처리장치 메이저 상태 (CPU Major State)

I. CPU의 4가지 작업상태, 중앙처리장치의 메이저 상태 개요

가. 중앙처리장치의 메이저 상태 정의

- CPU가 현재 수행하는 4가지 형태( Fetch, Indirect, Execute, Interrupt )의 작업 상태

나. 메이저 상태의 특징

- CPI는 4가지 상태를 반복적으로 수행, 메이저 상태 레지스터를 통해 확인

II. 메이저 상태 개념도 및 설명

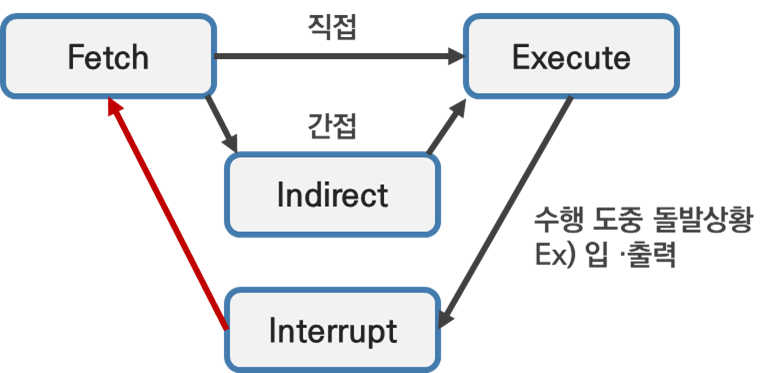

가. 메이저 상태 개념도

|

나. 메이저 상태 설명

| 메이저 상태 | 역할 | 동작 과정 |

| Fetch | - 명령어를 메모리에서 CPU 레지스터로 가져와서 해독 | MAR ← PC, PC에 있는 번지를 MAR에 전송 MBR ← M[MAR], 메모리에서 MAR이 지정하는 위치의 값을 MBR에 전송 PC ← PC + 1, 다음에 실행할 명령의 위치를 지정하기 위해 PC 값 1 증가 IR ← MBR[OP], 명령어의 OP-Code 부분을 명령 레지스터에 전송 I ← MBR[i], 명령어의 모든 비트를 플립플롭 I에 전송 F ← 1 or R ← 1, I가 0이면 F 플립플롭에 1을 전송하여 Execute 단계로 전환하고 I가 1이면 R 플립플롭에 1을 전송하여 Indirect 단계로 전환 |

| Indirect | - Fetch 단계에서 해석된 명령어의 주소부가 간접 주소인 경우 수행 | MAR ← MBR(Address), MBR에 있는 명령어의 번지 부분을 MAR에 전송 MBR ← M[MAR], 메모리에서 MAR이 지정하는 위치의 값을 MBR에 전송 No Operation, 동작없음 F ← 1 / R ← 0, F에 1, R에 0을 전송하여 Execute 단계로 전환 |

| Execute | - Fetch 단계에서 인출해 해석한 명령을 실행하는 단계 - 플래그 레지스터의 상태변화를 검사해 Interrupt 단계로 이동할지 판단 - Interrupt 요청 신호를 나타내는 플래그 레지스터의 변화가 없으면 Fetch 단계로 이동 |

MAR ← MBR(Address), MBR에 있느 ㄴ명령어의 번지 부분을 MAR에 전송 MBR ← M[MAR], 메모리에서 MAR이 지정하는 위치의 값을 MBR에 전송 AC ← AC + MBR, 누산기의 값과 MBR의 값을 더해 누산기에 전송 F ← 1 or R ← 0, F에 0을 전송하면 F=0, R=0이 되어 Fetch 단계로 전화하고 R에 1을 주면 F=1, R=1이 되어 Interrupt 단계로 전환한다. |

| Interrupt | - Interrupt 발생 시 복귀 주소(PC)를 저장하고, 제어 순서를 인터럽트 처리 프로그램의 첫번 째 명령으로 옮기는 단계 | MBR(Address) ← PC, PC가 가지고 있는 다음에 실행할 명령의 주소를 MBR의 주소 부분으로 전송 PC ← 0, 복귀 주소를 저장할 0번지를 Pc에 전송 MAR ← PC, PC가 가지고 있는 값 0번지를 MAR에 전송 PC ← PC + 1, ISR로 이동할 수 있는 IV의 위치를 지정하기 위해 PC의 값을 1증가시켜 1로 세트 M[MAR] ← MBR, MBR이 가지고 있는 다음에 실행할 명령의 주소를 메모리의 MAR이 가리키는 위치(0버지)에 저장 IEN ← 0, 인터럽트 단계가 끝날 때까지 다른 인터럽트가 발행되지 않게 IEN에 0을 전송 F ← 0 / R ← 0, Execute Cycle은 F와 R 플립플롭 상태가 F = 1, R = 0이고 F에 0을 전송하면 F=0, R=0이 디어 Fetch 단계로 전환된고 R에 1을 주면 F=1, R=1이 되어 Interrupt 단계로 전환 |

- 인터럽트 발생 시 발생 인터럽트 ID를 IVT(Interrupt Vector Table)에서 조회후 해당하는 처리 루틴으로 분기

III. 중앙처리장치 메이저 상태 변화 과정

| 상황 | 변화과정 |

| 직접 주소 사용 시 | - 인출 사이클 → 실행 사이클 |

| 간접 주소 사용 시 | - 인출 사이클 → 간접 사이클 → 실행 사이클 |

| 인터럽트 발생 시 | - 인출 사이클 → 간접 사이클 → 실행 사이클 → 인터럽트 발생 → 인터럽트 사이클 → 인출 사이 |

※ 용어 참고

| 용어 | 설명 |

| MAR, Memory Address Register | - PC 에 저장된 명령어 주소가 사용되기 전에 일시적으로 저장되는 주소 레지스터 |

| MBR, Memory Buffer Register | - 기억장치에 저장될 데이터 혹은 읽혀진 데이터가 일시적으로 저장되는 버퍼 레지스터 |

| PC, Program Counter | - 다음 인출(Fetch) 될 명령어의 주소를 가지고 있는 레지스터 |

| IR, Instruction Register | - 현재 수행 중인 명령을 갖고 있는 레지스터 |

| OP, Operation Code | - 수행할 연산 |

| AC, Accumulator | - 연산 결과 데이터를 일시적으로 저장하는 레지스터 |

| SP, Stack Pointer | - 주기억장치 스택의 데이터 삽입과 삭제가 이루어지는 주소를 저장 |

| ISR, Interrupt Service Routine | - 인터럽트 처리 동작 수행 |

- 레지스터는 주기억장치로부터 읽어온 명령어나 데이터를 저장하거나 연산된 결과를 저장하는 공

반응형

'IT기술노트 > 컴퓨터구조 및 운영체제' 카테고리의 다른 글

| FCFS 스케쥴링 (First Come First Service Scheduling) (0) | 2024.03.13 |

|---|---|

| 교착 상태(Dead Lock) 발생의 필수조건과, 교착 상태 해결방안 (3) | 2023.11.25 |

| GPGPU(General Purpose Graphic Processing Units) (0) | 2023.10.19 |

| IPC, Inter-Process Communication (0) | 2023.10.12 |

| 모니터 (Monitor) (0) | 2022.07.28 |

| 세마포어 (Semaphore) (0) | 2022.07.28 |

| 뉴로모픽 칩(Neuromorphic Chip) (0) | 2022.07.04 |

| DAS, NAS, SAN (0) | 2022.06.29 |

댓글